FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

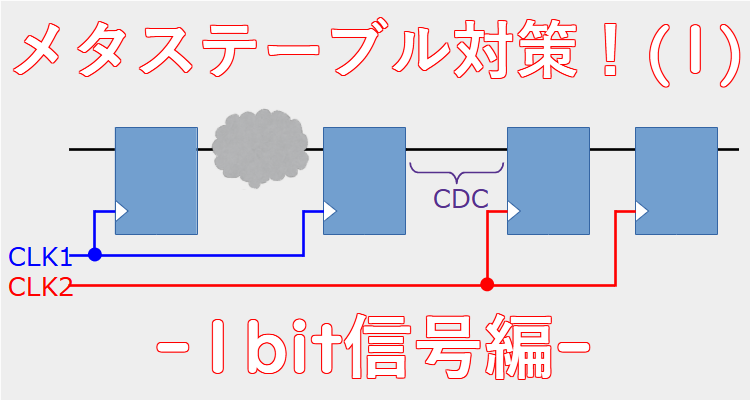

今回は、FPGAの不具合の原因となるメタステーブル(metastable)の対策について解説します。この回では1bitの信号における対策を解説します。

目次

「メタステーブルはどんなときに発生する?」の記事で解説したように、非同期クロック間でのデータ受け渡し(転送)でメタステーブルが発生します。また、非同期クロック間でのデータ受け渡し(転送)のことを、クロック・ドメイン・クロッシング(Clock Domain Crossing: CDC)といいました。

関連記事

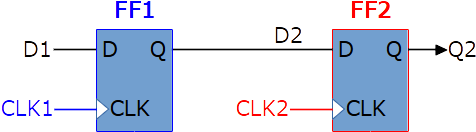

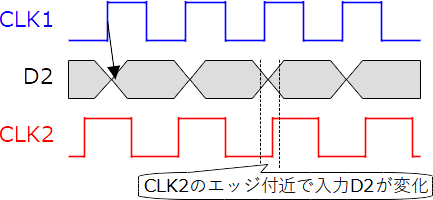

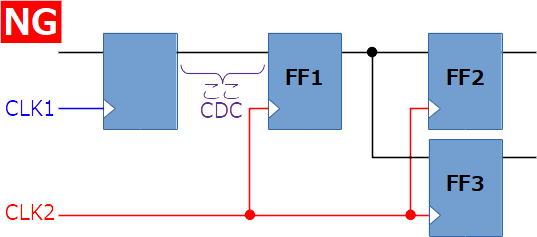

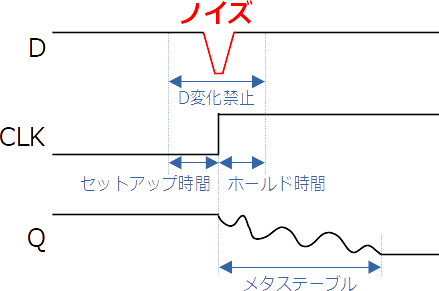

図1のようにCLK1で動くフリップフロップFF1と、CLK2で動くフリップフロップFF2でデータ受け渡しを行うと、図2のようにセットアップ時間またはホールド時間が守られない位相になることがあります。すると、図3のようにメタステーブルが発生します。

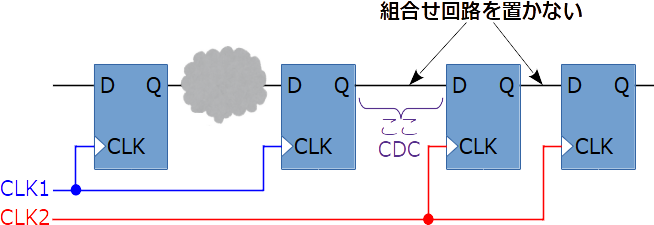

図4にメタステーブル対策の例を示します。

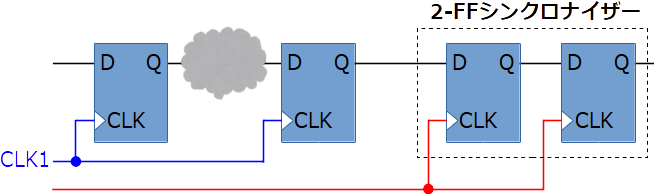

CLK2でデータを受け取った後の2段のフリップフロップのことを、2-FFシンクロナイザー(2-FF Synchronizer)といいます。

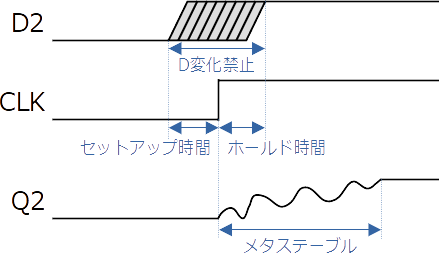

メタステーブルによる発振は永遠に続くわけではなく、ある程度の時間で1か0に収束します。したがって、2-FFの2段目で時間稼ぎをし、2段目がデータを受け取った次のクロックエッジまでにデータが1か0に収束していれば、以降の回路には影響を与えません。

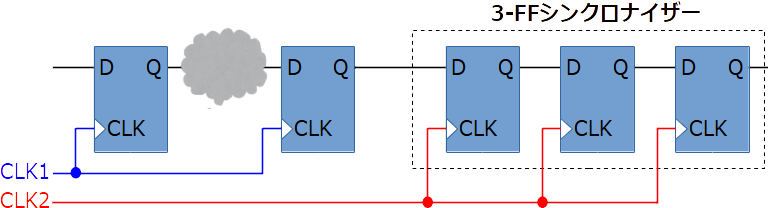

非同期クロック間でのデータ受け渡しでは、図4、図5のような2-FFシンクロナイザーがよく使われます。リセット生成回路など、システム上特にセンシティブであったり重要であったりする部分には、図6のような3-FFシンクロナイザーや、さらに増やした4-FFシンクロナイザーが使われる場合もあります。

これらを一般化して、m-FFシンクロナイザー(m-FF Synchronizer)といいます。

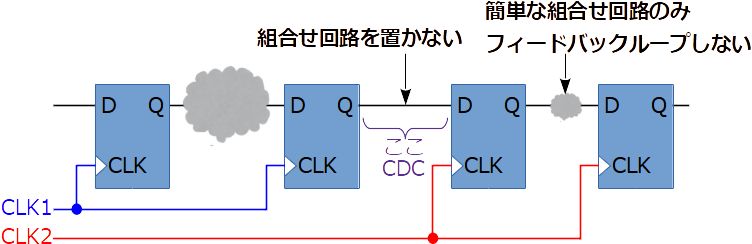

CLK1とCLK2の周波数が低い場合は、図7のように1段目のフリップフロップと2段目のフリップフロップの間に多少の組合せ回路をがあってもよいです。ただし、図8のようにデータ保持のためのフィードバックループがあると問題になります。メタステーブルが入力されることで、保持している値を壊してしまう可能性があるためです。

周波数が低い場合は図7のような回路でも実動作上問題は起こらないかもしれませんが、レビューなどで問題の無い回路か判断するのは難しくなります。したがって、非同期クロック間のデータ受け渡しでは、必ずm-FFシンクロナイザーを使うように設計することをオススメします。

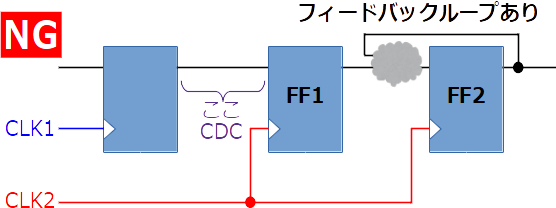

図8、図9にダメな例を示します。

図8では、非同期クロック間のデータ受け渡し直後にデータ保持のためのフィードバックループがあります。FF1の出力はメタステーブルになる可能性がり、FF2で保持している値を壊してしまう可能性があります。

図9では、非同期クロック間のデータ受け渡しの後、複数のフリップフロップでデータを使っています。FF1の出力はメタステーブルになる可能性があります。FF2、FF3は同じデータを使うつもりで設計されていますが、メタステーブルが入力されることで、一方は0を出力、もう一方は1を出力となってしまう可能性があります。

FPGA外部からの入力信号は、ノイズが乗る可能性があります。すると、図10のようにメタステーブルが発生する可能性があります。近年はI/O電圧が低電圧化しているため、ノイズに対してより敏感になっています。FPGA外部からの入力はm-FFシンクロナイザーで受けるようにしましょう。

以上で説明したm-FFシンクロナイザーは1bitの信号のみに有効です。多ビットの信号(バス)には別の対策が必要です。これらは別途解説します。