FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

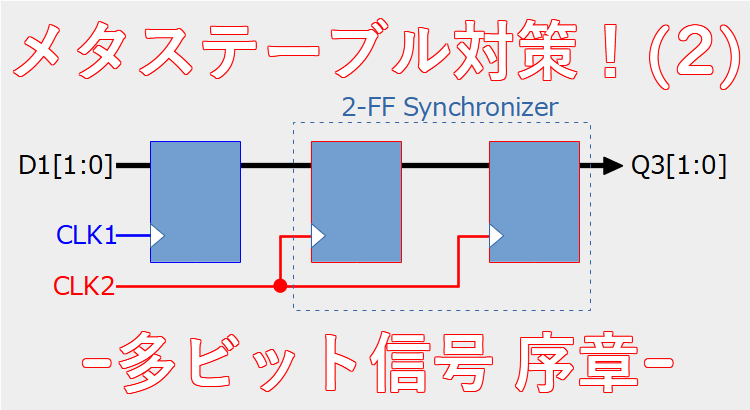

メタステーブル対策!第2回~第4回は、多ビット信号(バス)のメタステーブル(metastable)対策について解説していきます。この回では、多ビット信号では単純にm-FFシンクロナイザーを使うことはできないという話をします。

目次

メタステーブル対策!第1回の記事で解説したように、1ビットの信号であれば、m-FFシンクロナイザーを置くことで、非同期クロック間のデータ受け渡し(Clock Domain Crossing: CDC)ができました。

その中でもよく使われているのは、2-FFシンクロナイザー(2-FF Synchronizer)でした。

関連記事

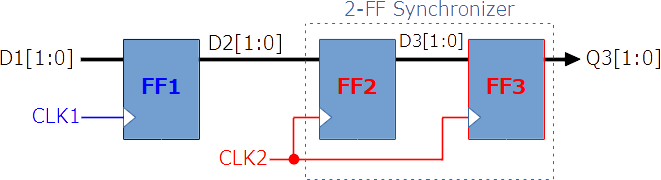

2ビット信号でのCDCを考えます。ブロック図は一般的に図1のように描かれます。CLK2で動作する2つのフリップフロップ(FF2とFF3)が2-FFシンクロナイザーです。

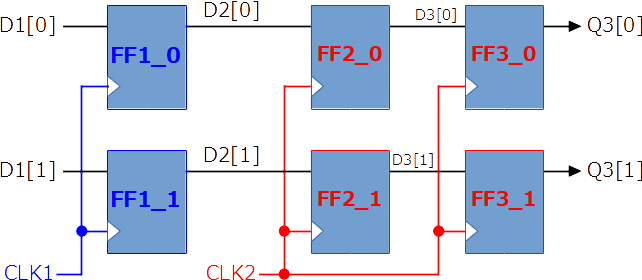

フリップフロップは1ビットの記憶素子ですので、実際の回路は図2のようになります。同じ回路が、0ビット目と1ビット目それぞれについて、パラレルで存在することになります。

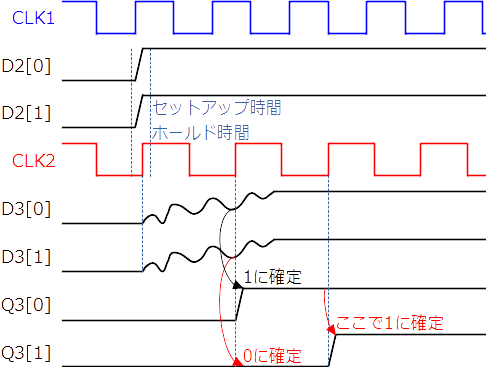

このときの信号波形は図3のようになります。

ここ、重要です。

FF2_0とFF2_1の出力である、D3[0]とD3[1]はメタステーブルになる可能性があります。そして、FF3_0とFF3_0にはメタステーブルが入力されます。このとき、FF3_0とFF3_1の出力は、1または0のどちらかに確定します。どちらになるかはわかりません。次のサイクルでは、どちらのビットもとるべき値(図3の場合は1)に確定します。

つまり、多ビット信号でm-FFシンクロナイザーを通した後は、どこかのビットが1クロックだけずれる可能性があります。

図3においては、

Q3を使う後段の回路が、0x1の瞬間で値を使うと、不具合が発生してしまいます。

したがって、多ビット信号では単純にm-FFシンクロナイザーを使えばよいということではありません。多ビット信号用の対策が必要となります。具体的な対策については次回解説します。