FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

今回は、多ビット信号(バス)の非同期クロック間のデータ受け渡し(Clock Domain Crossing: CDC)方法について説明します。

目次

多ビット信号のCDCでは、「これだけやればよい」という方法はありません。設計するシステムによって、最適な方法を選択する必要があります。よく使われる方法としては、

などがあります。

今回は、フリップフロップを使った回路による方法の例を2つ説明します。

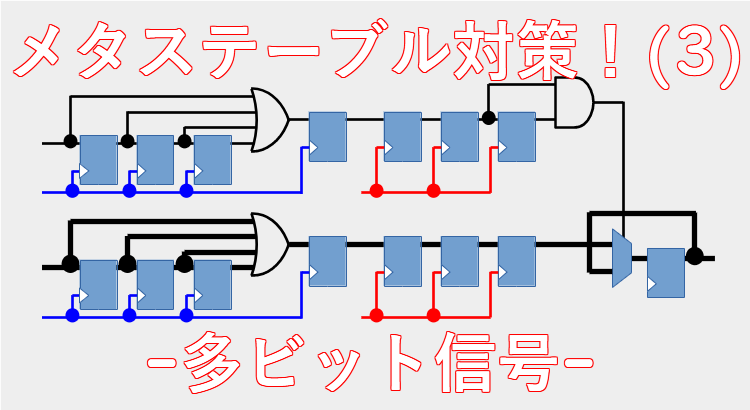

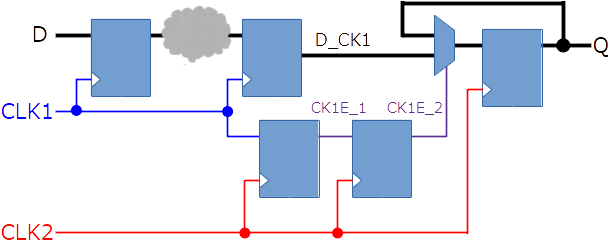

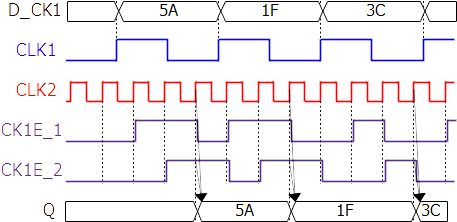

図1に、周波数が低いクロックCLK1から、周波数が高いクロックCLK2にデータを受け渡す回路を示します。図2にタイミングチャートを示します。

これは、CLK1をCLK2でラッチする方法です。図1のように、CLK1をCLK2でラッチした信号をセレクト信号にします。この回路では、CLK2の周波数がCLK1の周波数の3倍以上であればビット化けせずにデータを受け渡すことができます。

この方法は、小さい回路規模で実現できます。ハンドシェイクやFIFOに比べればかなり簡易的な方法です。

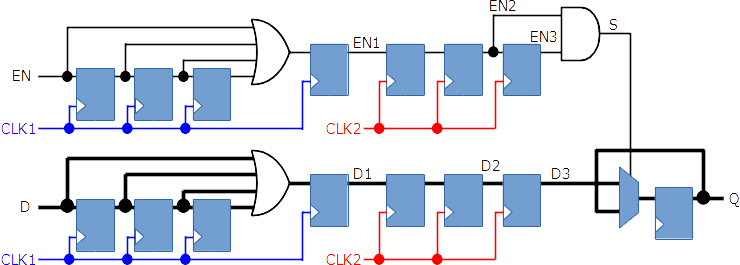

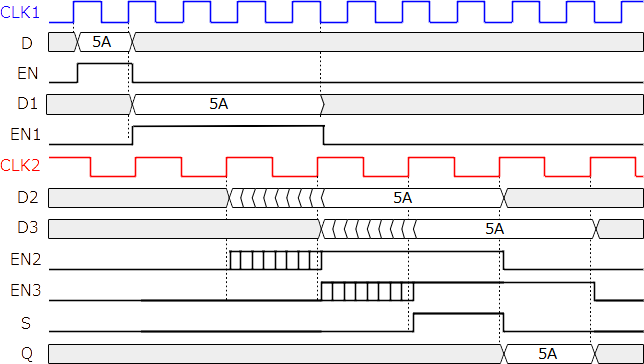

図3に、周波数が高いクロックCLK1から、周波数が低いクロックCLK2にデータを受け渡す回路を示します。図4にタイミングチャートを示します。

まず、低周波のクロックで受け取れるだけの時間、データを固定しておきます。これは前半のフリップフロップ3段、ORゲート、EN1, D1を出力するフリップの部分です。なお、ORゲートまでで、データの時間を長くできそうです。しかし、EN1, D1を出力するフリップは必ず必要です。理由は別途解説します。

低周波のクロックCLK2でデータを受け取った後、メタステーブル対策のためフリップ2段を入れ、その出力はEN2, D2となります。データ信号が確実に確定しているタイミングでデータを取り込むため、信号Sをつくります。この信号Sが1になったとき、データをラッチしQに出力します。

この回路では、CLK1とCLK2の周波数の比率により、回路を変える必要があります。例えば、CLK1がもっと高周波であれば、前段のフリップフロップの数を増やす必要があります。

また、低周波→高周波の回路とは異なり、CLK1側で連続して変化するデータの転送はできません。

今回は、多ビット信号(バス)の非同期クロック間のデータ受け渡し(CDC)を行う回路の例を示しました。多ビット信号では、「これだけやればよい」という方法は無いので、今回のような回路を参考に、システムに最適な回路を構築していただければと思います。