FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

今回は、多ビット信号(バス)の非同期クロック間のデータ受け渡し(Clock Domain Crossing: CDC)方法について説明します。

目次

多ビット信号のCDCでは、「これだけやればよい」という方法はありません。設計するシステムによって、最適な方法を選択する必要があります。

メタステーブル対策!第3回では、フリップフロップを使った回路による方法を紹介しました。

今回は、

を紹介します。

関連記事

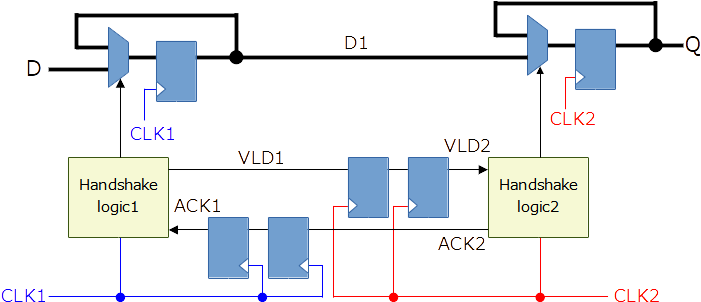

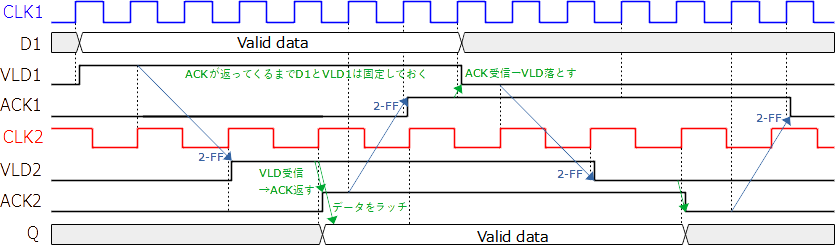

図1にハンドシェイクによるCDCの回路、図2に波形を示します。

簡単に言うと、受け取る側が「受け取ったよ」と言うまで、送る側がデータを固定する、という方法です。

以上のように、VLDとACKのやり取りによって、多ビット信号を安全に受け渡すことができます。この方法は、連続して変化するデータを渡すことはできません。

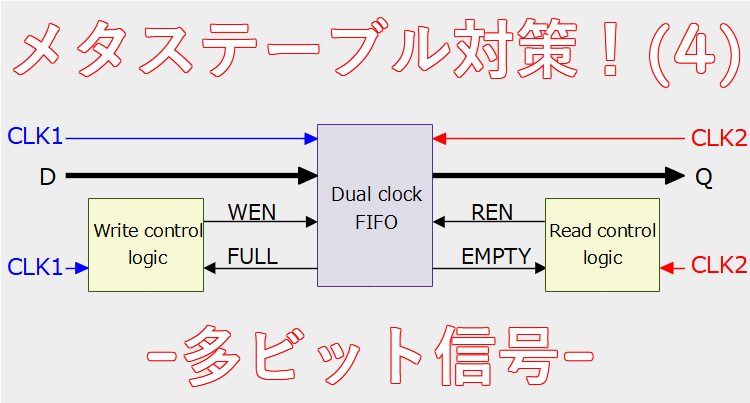

次に、FIFOによるCDCを紹介します。FIFOは、First In, First Outの略です。図3のように、先に入ったデータから先に読み出すメモリーです。順番待ちの行列や、ところてんのようなイメージです。

FIFOのクロックは、書き込み(Write側)と読み出し(Read側)で、異なるクロックを使うことができます。これにより、異なるクロック間のデータ受け渡しが実現できます。FIFOはもちろんユーザーがロジックを組むことができますが、FPGAメーカーがIPを用意しているので、これを使うと便利です。

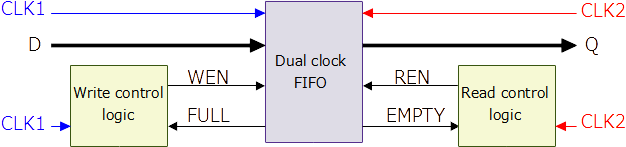

FIFOを使ったCDCの回路は図4のようになります。同図のDual clock FIFOはWENがアサートされるとデータが書き込まれ、RENがアサートされるとデータを出力します。

FIFOに貯められるデータの量は有限ですので、満タンになったことを通知するFULL出力があります。Write側は、FULLを見て書き込みを一時ストップするなどの制御を行います。

一方、FIFOにデータが1つも無いことを通知するEMPTY出力もあります。Read側は、EMPTYを見て読み込みをストップするなどの制御を行います。EMPTYがアサートされているときに読み込みを行うと、不正なデータが読めます。