FPGAが時々動かない??-ステート・マシンのデッドロック-

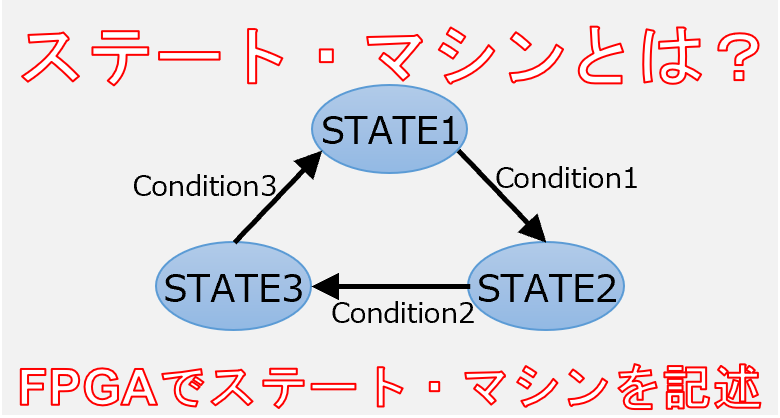

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

今回は、ビット化けの原因であるメタステーブル(metastable)がどんなときに発生するのかを解説します。FPGAを安定して動作させるために重要な考え方です。

セットアップ時間・ホールド時間が守られないとメタステーブルが発生するわけですが、どんなときにセットアップ時間・ホールド時間が守られなくなるでしょうか。

目次

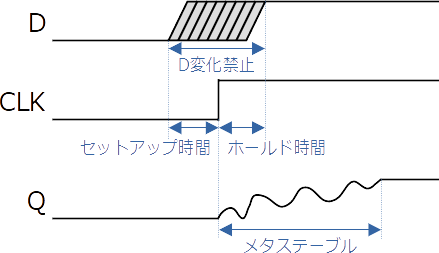

FPGA内で値を保持するフリップフロップ(Flip Flop)は、入力Dを変化させてはいけない時間があります。

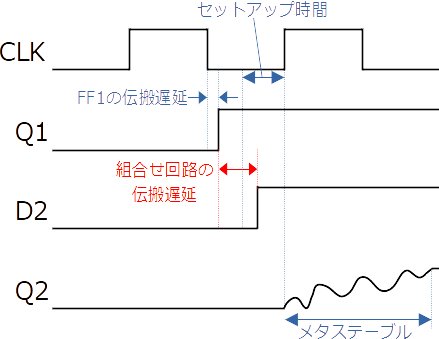

セットアップ時間、ホールド時間とメタステーブルの波形を図1に示します。メタステーブルは安定するのに時間がかかるため、同図の次のサイクルでQを使いたいフリップフロップがデータを取り損なうことがあります(1を取るはずのところが、0を取ってしまう。またはその逆)。

通常、論理合成ツールがセットアップ時間、ホールド時間が守られるように配置・配線しようとしてくれます。論理合成ツールはIntel→Quartus、Xilinx→Vivadoのことです。

しかし、それでもセットアップ時間、ホールド時間が守られなくなる状況について、代表的な2つを見ていきましょう。

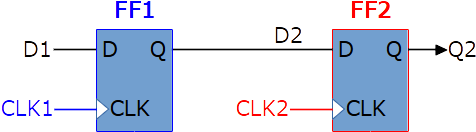

図2のような回路を考えます。前段のフリップフロップFF1はクロックCLK1で動作し、後段のフリップフロップFF2はクロックCLK2で動作します。

CLK1とCLK2は周波数が異なります。2つのクロックの位相差が管理されているときは同期、管理されていなくて、どんな位相差になるかわからないときは非同期といいます。設計する上では、異なるクロックであれば、たとえ周波数が同じでも非同期と考えて扱うのが安全です。

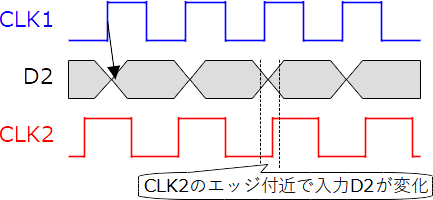

図3で、非同期クロック間のデータの受け渡しを見てみましょう。FF1はCLK1の立ち上がりエッジで入力D1を取り込み、D2に出力します。したがって、FF2の入力であるD2は、CLK1の立ち上がりエッジのタイミングで変化します。

FF2はCLK2で動作しているため、CLK2の立ち上がりエッジに対してセットアップ時間、ホールド時間が規定されています。CLK1とCLK2はどんな位相差になるかわからないため、図3の中央のように、FF2のセットアップ時間、ホールド時間が守られないような位相差になる場合があります。

このとき、FF2の出力Q2はメタステーブルとなり、次のサイクルでQ2を使うフリップフロップは正しくデータを取れなくなります。

なお、このような異なるクロック間のデータ受け渡しのことをクロック・ドメイン・クロッシング(Clock Domain Crossing: CDC)といいます。

FPGA内をすべて1つのクロックで動作させれば、CDCはありません。しかし、それは難しいのです。理由は、規格によって周波数が決められているためです。例えば、Ethernetなら25MHzの倍数、USBなら6MHzの倍数のクロックで動作させる場合が多いです。FPGAを使って、Ethernet-USB変換みたいなものをつくると、CDCが発生することになります。

図4の順序回路を考えます。FF1の出力Q1が、組合せ回路に入り、組合せ回路の出力D2がFF2に入力されます。なお、同図中の雲のような図は「何らかの組合せ回路」としてよく使われます。

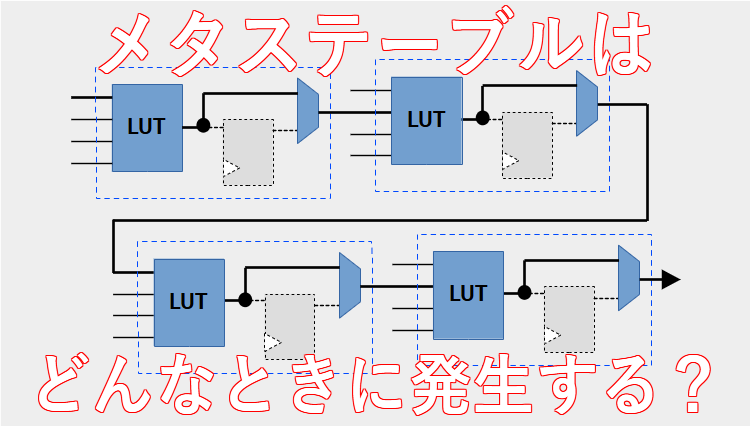

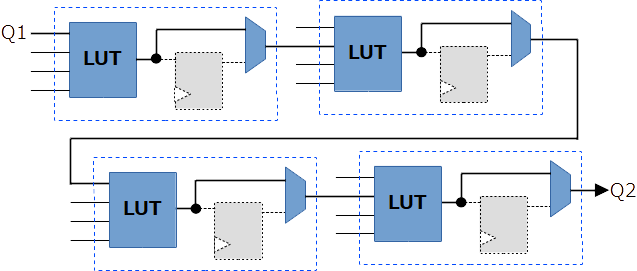

組合せ回路はLUTで実装されますが、論理が複雑であったり、多ビットであったりすると、沢山のLUTを経由することになります。図5のイメージです。このような組合せ回路を大きい組合せ回路と表現します。

関連記事

大きい組合せ回路では、沢山のLUTを経由するため、伝搬遅延が大きくなります。すると、図6のようにセットアップ時間が満足できなくなり、メタステーブルが発生します。