FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

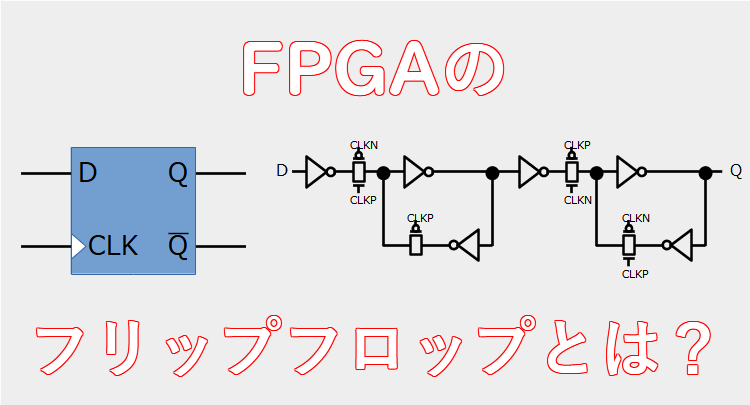

今回は、FPGAを構成する重要な要素の1つである、フリップフロップ(Flip Flop: FF)について解説していきます。

目次

まずは、なぜフリップフロップが必要なのかから説明します。それは、順序回路(sequential circuit)を実現するためです。

順序回路は、記憶素子を含む回路です。一方、記憶素子を含まず、論理ゲートの組み合わせのみで作られた回路を組合わせ回路といいました。

関連記事

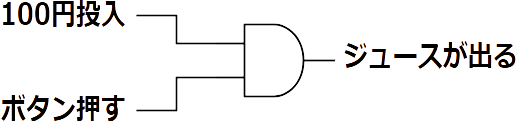

ではなぜ記憶素子が必要なのでしょうか。自動販売機を例に見てみましょう。

組み合わせ回路はその時点の入力のみにより、出力が決まります。したがって、組み合わせ回路だけで自動販売機をつくると図1のようになります。これでは、100円を入れるのと同時にボタンを押す必要があるので、かなりシビアです。

150円のジュースになると、もはや不可能ですね。

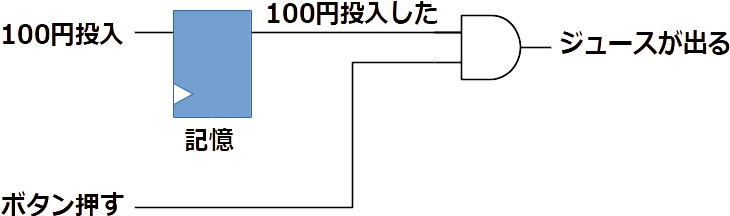

記憶素子がある場合は図2のようになります。これであれば、100円投入→ボタンを押す、と順番にやればジュースが手に入るわけです。

このように、記憶素子を含む回路を順序回路といいます。

FPGAでは、記憶素子として、フリップフロップ(Flip Flop: FF)が使われています。フリップフロップは1ビットの記憶素子です。

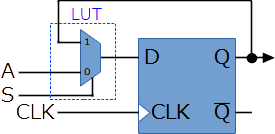

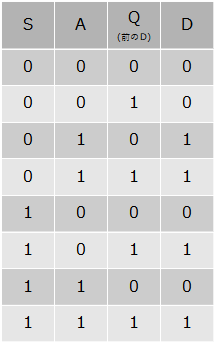

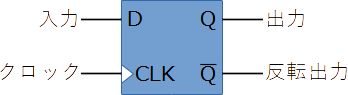

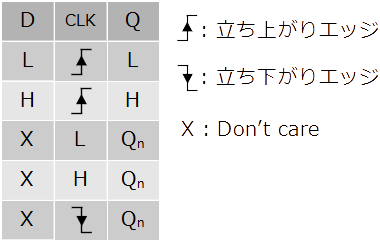

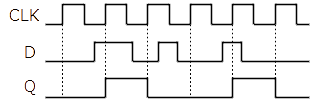

FPGAの論理ブロックに組み込まれているDフリップフロップ(D-FF)のシンボルと真理値表を図3、図4に示します。DフリップフロップはクロックCLKの立ち上がりのとき、入力Dを取り込み、Qに出力します。クロックがそれ以外のときは、Qは変化せず値を保持します。動作例を図5に示します。

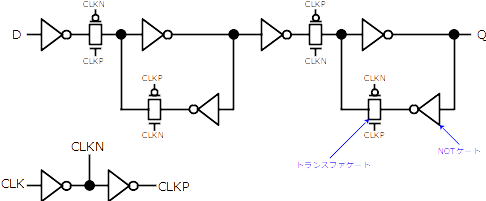

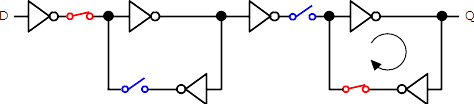

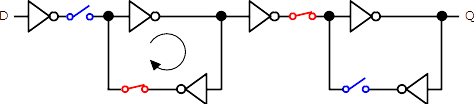

Dフリップフロップの内部構造は図6のようになっています。トランスファゲートはCLKの状態によってONまたはOFFになるスイッチです。ループ回路が前段、後段と2段になった構成をしています。

Dフリップフロップの動作を図7に示します。

CLK = 0のときは、前段に入力Dが入り、後段では前サイクルの値をループし保持します。このとき、前段と後段の間のトランスファゲートがOFFなので、入力Dは後段には伝わりません。

CLK = 1になったとき、入力Dが取り込まれて後段に伝わるとともに、前段でループし保持します。その後、CLK = 1の状態では入力直後のトランスファゲートがOFFとなるので、入力を変化させても伝わりません。

以上のようにして、クロックの立ち上がりエッジ(CLK = 0 → 1の変化時)に入力Dを取り込み、次のクロックの立ち上がりまで保持するという動作を実現します。

ここまでの説明で、たった1クロックサイクルの間しか保持できないに、そんなの使えるの?と思った方もいるかと思います。大丈夫です。例えば、図8のような回路にすれば、スイッチ入力Sが1である間は前に取り込んだ値を保持し続けます。スイッチの論理はLUTで実現されます。