UVMの環境構築!(10) Test (テストコンポーネント)

UVMの環境構築!(9) Environment

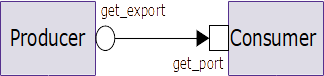

第2回~第4回では、UVMにおける、TLMによるコンポーネント間の通信の例を示します。今回は、get_port/get_exportを使用した例を示します。TLMの解説は、第1回 解説編をご覧ください。

関連記事

なお、ソースコードはGitHubに公開しています。

目次

トランザクションはuvm_sequence_itemを継承して作成します。第1回 解説編 の記事で解説したものと同じものを使います。

(1) simple_transaction.sv

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 | class simple_transaction extends uvm_sequence_item; rand bit[7:0] data_e; rand bit[7:0] data_o; constraint CE { data_e[0] == 1'b0; } // Even number constraint CO { data_o[0] == 1'b1; } // Odd number `uvm_object_utils_begin(simple_transaction) `uvm_field_int(data_e, UVM_DEFAULT) `uvm_field_int(data_o, UVM_DEFAULT) `uvm_component_utils_end function new (string name = "simple_transaction"); super.new(name); endfunction endclass |

UVMのコンポーネントは3個です。

(2) get_consumer.sv

uvm_blocking_get_port#(T) により、get_portを定義します。run_phaseにて、get_port.get( )を呼び、Get動作を発生させます。14行目です。これを、for文で5回繰り返します。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 | class get_consumer extends uvm_component; uvm_blocking_get_port #(simple_transaction) get_port; `uvm_component_utils(get_consumer) function new(string name, uvm_component parent); super.new(name, parent); get_port = new("get_port", this); endfunction task run_phase(uvm_phase phase); simple_transaction data; for (int i = 0; i < 5; i++) begin `uvm_info("CONSUMER", $sformatf("Getting data... i = %d", i), UVM_LOW) get_port.get(data); // Initiate getting a transaction `uvm_info("CONSUMER", $sformatf("Got: data_e = %d, data_o = %d", data.data_e, data.data_o), UVM_LOW) end endtask endclass |

(3) get_producer.sv

uvm_blocking_get_imp#(T, IMP) により、get_exportを定義します。task get( )の動作を定義します。トランザクションを生成、randomizeして送信します。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 | class get_producer extends uvm_component; uvm_blocking_get_imp #(simple_transaction, get_producer) get_export; `uvm_component_utils(get_producer) function new(string name, uvm_component parent); super.new(name, parent); get_export = new("get_export", this); endfunction task get(output simple_transaction data); // Define behavior of get() data = simple_transaction::type_id::create("data"); assert (data.randomize()); `uvm_info("PRODUCER", $sformatf("Made: data_e = %d, data_o = %d", data.data_e, data.data_o), UVM_LOW) endtask endclass |

(4) get_parent.sv

build_phaseでget_consumerとget_producerをインスタンスし、connect_phaseでget_portとget_exportを接続します。21行目です。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 | class get_parent extends uvm_component; get_consumer consumer; get_producer producer; `uvm_component_utils(get_parent) function new(string name, uvm_component parent); super.new(name, parent); endfunction function void build_phase(uvm_phase phase); super.build_phase(phase); consumer = get_consumer::type_id::create("consumer", this); producer = get_producer::type_id::create("producer", this); endfunction function void connect_phase(uvm_phase phase); super.connect_phase(phase); consumer.get_port.connect(producer.get_export); endfunction endclass |

(5) pkg.sv

作成したすべてのclassをpackageにしておきます。次のtop.svのように、importして使うことで、すっきりした記述になります。

1 2 3 4 5 6 7 8 9 10 11 12 13 | package pkg; `include "uvm_macros.svh" import uvm_pkg::*; /* Include transactions */ `include "simple_transaction.sv" /* Include classes */ `include "get_consumer.sv" `include "get_producer.sv" `include "get_parent.sv" endpackage |

(6) top.sv

get_parentのインスタンスを生成し、run_testします。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 | `include "uvm_macros.svh" `include "pkg.sv" module top(); import uvm_pkg::*; import pkg::*; get_parent parent; initial begin `uvm_info("INFO", "get port test", UVM_LOW) parent = get_parent::type_id::create("parent", null); run_test(); end endmodule |

Vivado Simulatorで動作します。実行の手順はこちらの記事をご覧ください。QuestaとModelSimで行うためには有料版が必要です。randomize( )機能は有料版でないと使えないようです。

Printされた内容はTcl Consoleに出力されます。get_producerから送信したトランザクションが、get_consumerでちゃんと受け取れていることが確認できます。

UVM_INFO C:/sim_1/get_consumer.sv(21) @ 0: parent.consumer [CONSUMER] Getting data… i = 0

UVM_INFO C:/sim_1/get_producer.sv(20) @ 0: parent.producer [PRODUCER] Made: data_e = 48, data_o = 87

UVM_INFO C:/sim_1/get_consumer.sv(25) @ 0: parent.consumer [CONSUMER] Got: data_e = 48, data_o = 87

UVM_INFO C:/sim_1/get_consumer.sv(21) @ 0: parent.consumer [CONSUMER] Getting data… i = 1

UVM_INFO C:/sim_1/get_producer.sv(20) @ 0: parent.producer [PRODUCER] Made: data_e = 164, data_o = 75

UVM_INFO C:/sim_1/get_consumer.sv(25) @ 0: parent.consumer [CONSUMER] Got: data_e = 164, data_o = 75

UVM_INFO C:/sim_1/get_consumer.sv(21) @ 0: parent.consumer [CONSUMER] Getting data… i = 2

UVM_INFO C:/sim_1/get_producer.sv(20) @ 0: parent.producer [PRODUCER] Made: data_e = 2, data_o = 227

UVM_INFO C:/sim_1/get_consumer.sv(25) @ 0: parent.consumer [CONSUMER] Got: data_e = 2, data_o = 227

…略…

今回は、get_port/get_exportの使用例を示しました。ポートの生成、get( )メソッドの定義、ポートの接続については、参考にしていただけると思います。