UVMの環境構築!(9) Environment

UVMの環境構築!(8) Scoreboard

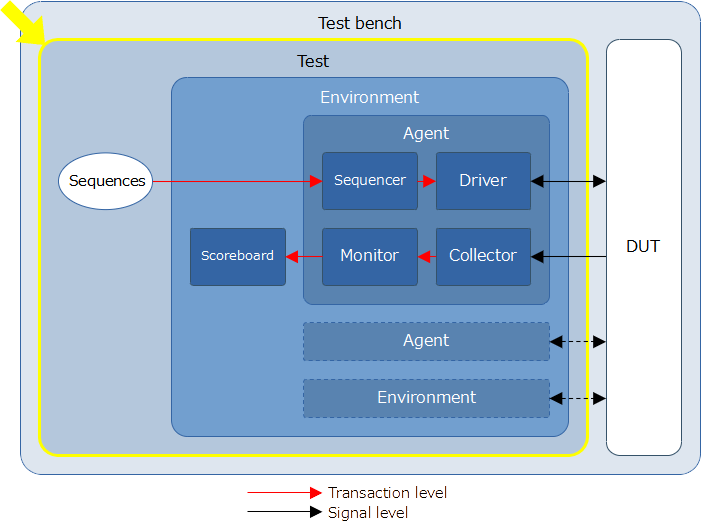

UVMの環境構築第9回では、テストの定義(作成)方法について解説していきます。

なお、ソースコードはGitHubに公開しています。

目次

UVMの環境構築!シリーズの目次は、第1回 解説編の一番下をご覧ください。

テスト(テストコンポーネント)はuvm_testまたはそのサブクラスを継承して定義します。

テストコンポーネントの目的は、テスト項目を指定することです。主に次のことを行います。

通常は複数のテストケースがあり、その中で共通する項目があります。したがって、共通する項目をベースクラスとして定義し、そのベースクラスを継承して各テストケースを定義します。

それでは、ソースコードを見ながら、テストの定義方法について説明します。

my_test_base.sv

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 | class my_test_base extends uvm_test; my_env env0; string result; `uvm_component_utils(my_test_base) /* Constructor */ function new(string name = "my_test_base", uvm_component parent = null); super.new(name, parent); endfunction /* Build phase */ function void build_phase(uvm_phase phase); super.build_phase(phase); env0 = my_env::type_id::create("env0", this); endfunction /* Extract phase */ function void extract_phase(uvm_phase phase); if (env0.scoreboard0.n_error > 0) result = "FAIL"; else result = "PASS"; endfunction /* Report phase */ function void report_phase(uvm_phase phase); `uvm_info(get_type_name(), $sformatf("[%s] Trial = %d, Error = %d", result, env0.scoreboard0.n_trial, env0.scoreboard0.n_error), UVM_NONE) endfunction endclass |

/* Build phase */ function void build_phase(uvm_phase phase); super.build_phase(phase); uvm_config_db#(T)::set(this, "env0", "config_pram1", value1); uvm_config_db#(T)::set(this, "env0", "config_pram2", value2); env0 = my_env::type_id::create("env0", this); endfunction |

通常は複数のテストケースがありますが、今回は1つだけテストケースを定義しました。

my_test1.sv

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | class my_test1 extends my_test_base; `uvm_component_utils(my_test1) /* Constructor */ function new(string name = "my_test1", uvm_component parent = null); super.new(name, parent); endfunction /* Build phase */ function void build_phase(uvm_phase phase); uvm_config_db #(uvm_object_wrapper)::set( this, "env0.agent0.sequencer.run_phase", "default_sequence", my_sequence1::type_id::get() ); super.build_phase(phase); endfunction endclass |

今回はenv0とagent0しかないので、テストの役割が分かりにくいかもしれません。例えば、agent0とagent1があった場合、次のようにテストケースを作成できます。各コンポーネントとシーケンスを個別に作った後に複数のテストパターンを作成できるため、検証環境構築が効率的になります。

| agent0 に割り当てるシーケンス | agent1 に割り当てるシーケンス | |

| テストケース1 | シーケンスA_0 | シーケンスB_0 |

| テストケース2 | シーケンスA_0 | シーケンスB_1 |

| テストケース3 | シーケンスA_1 | シーケンスB_0 |

| テストケース4 | シーケンスA_1 | シーケンスB_1 |

今回は、テスト(テストコンポーネント)の定義方法について解説しました。シリーズを通してご覧いただけると、UVM検証環境が構築できるようになりますので、ぜひ他のコンポーネントの解説もご覧ください。

シリーズ目次はこちら