FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

今回は、FPGAのフリップフロップ(Flip Flop: FF)で発生する、メタステーブル(metastable)について解説します。また、これに関連して、セットアップ時間(setup time)とホールド時間(hold time)について解説します。FPGAを安定して動作させるために非常に重要です。

目次

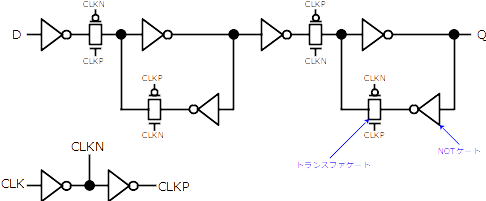

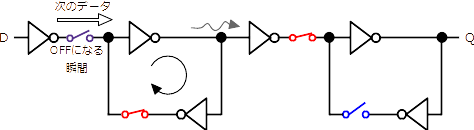

まずは、FPGAに組み込まれているDフリップフロップ(D-FF)の構造を図1に示します。

トランスファゲートはCLKの状態によってONまたはOFFになるスイッチです。ループ回路が前段、後段と2段になった構成をしています。

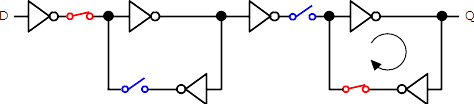

次に、Dフリップフロップの動作を図2に示します。

CLK = 0のときは、前段に入力Dが入り、後段では前サイクルの値をループし保持します。このとき、前段と後段の間のトランスファゲートがOFFなので、入力Dは後段には伝わりません。

CLK = 1になったとき、入力Dが取り込まれて後段に伝わるとともに、前段でループし保持します。その後、CLK = 1の状態では入力直後のトランスファゲートがOFFとなるので、入力を変化させても伝わりません。

以上のようにして、クロックの立ち上がりエッジ(CLK = 0 → 1の変化時)に入力Dを取り込み、次のクロックの立ち上がりまで保持するという動作を実現します。

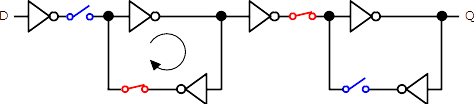

CLK = 0 → 1のとき、信号が前段のループを1周していないと、信号が0と1の間を揺れる中間電位状態になってしまいます(図3)。これがメタステーブルです。この状況を防ぐため、クロックエッジよりもある程度前に入力Dを固定し、変化させてはいけない時間があります。これがセットアップ時間です。

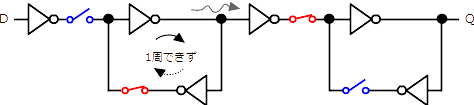

また、CLK = 1にしたとき、入力のトランスファゲートがOFFになる直前に入力Dが変化すると、その値を取り込んでしまいメタステーブルが発生します(図4)。この状況を防ぐため、クロックエッジからある程度後まで入力Dを固定しておく必要があります。この時間がホールド時間です。

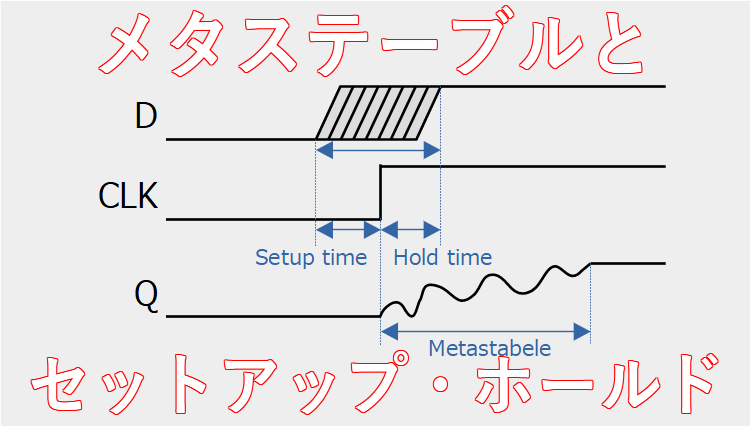

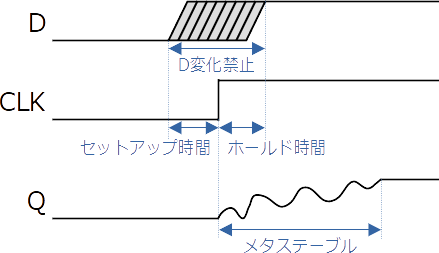

セットアップ時間、ホールド時間とメタステーブルの波形を図5に示します。メタステーブルからデータが0または1に確定するのは時間がかかります。通常、クロックエッジからQ出力までの伝搬遅延の規格値をオーバーします(安定までにとっても時間がかかるということ)。これにより、データを取り損なうことがあり、ビット化けが発生します。

図5の例では、図中のクロックエッジの次のサイクルで1を取りたいわけですが、次のサイクルまでメタステーブル状態が続くため、1を取り損なうことになります。

FPGAの設計では、メタステーブルが発生しないように、またはメタステーブルが発生しても問題ないようにする必要があります。どんなときににメタステーブルが発生するのかは、別途解説します。

関連記事