UVMの環境構築!(10) Test (テストコンポーネント)

UVMの環境構築!(9) Environment

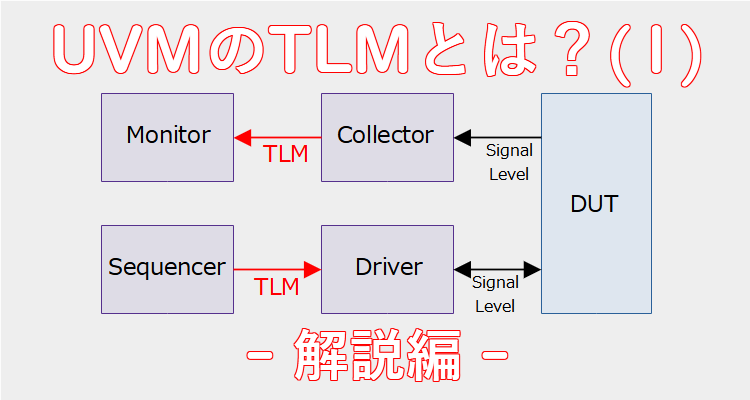

今回は、UVM (Universal Verification Methodology) のコンポーネント(機能ブロック)間の通信で使われる、TLMについて説明します。

目次

TLMは、Transaction Level Modelingの略です。TLM、回路記述で使われるシグナルレベルよりも高位の記述法です。

「高位」というのは、より人間の思考に近いということです。例えば、「アドレス0x0004に対して、データ0x1234をライトする」というかんじです。これに対してシグナルレベルは、例えば、「データをライトするために、valid信号をhighにして…ack信号を待って…」というかんじです。

TLMでやりとりされるデータのひとかたまりを、トランザクションといいます。

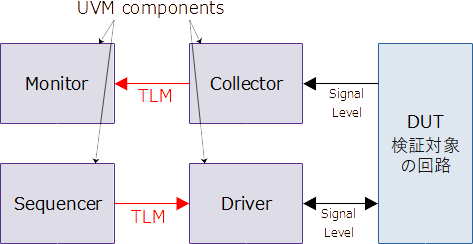

検証対象の回路はシグナルレベルで動作するので、UVMでは、トランザクションとシグナルレベルの変換をDriverとCollectorが行います。UVMコンポーネント間の通信はTLMであり、トランザクションのやりとりで行います(図1)。

TLMを使うためには、TLMのポートを定義して接続します。ポートの種類を表1に示します。

| ポート | 説明 |

| TLM port | 何らかのトランザクションに対する動作を発生させるポートです。これは、put( )メソッドやget( )メソッドの呼び出しをのことです。 |

| TLM export | 何らかのトランザクションに対する処理を定義します。TLM port側でput( )メソッドやget( )メソッドを呼ぶと、そのポートに接続されたTLM export側のput( )やget( )が呼ばれます。TLM export側では、この時の動作をタスクとして定義しておく必要があります。 |

| Analysis port | 1対Nの接続で使います。このポートが1側です。TLM portと同様に、動作を発生させるポートです。Analysis portでは、write( )メソッドの呼び出しを行います。 |

| Analysis export | 1対Nの接続で使います。このポートがN側です。接続されたAnalysis port側でwrite( )メソッドを呼ぶと、Analysis export側でwrite( )が呼ばれます。Analysis exportでは、write( )の処理を定義しておく必要があります。Analysis exportは複数個ある前提なので、時間を消費できません。したがって、ファンクションで処理を定義します。 |

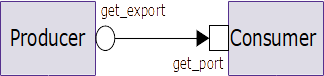

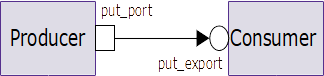

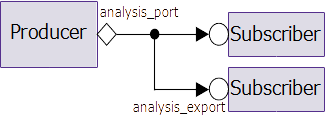

図2にTLMポートの記号と接続を示します。TLM portは□(四角)、Analysis portは◇(菱形)、TLM exportとAnalysis exportは○(丸)で示します。

トランザクションはuvm_sequence_item (またはそのサブクラス) を継承して定義します。

例を示します。

simple_transaction.sv

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 | class simple_transaction extends uvm_sequence_item; rand bit[7:0] data_e; rand bit[7:0] data_o; constraint CE { data_e[0] == 1'b0; } // Even number constraint CO { data_o[0] == 1'b1; } // Odd number `uvm_object_utils_begin(simple_transaction) `uvm_field_int(data_e, UVM_DEFAULT) `uvm_field_int(data_o, UVM_DEFAULT) `uvm_component_utils_end function new (string name = "simple_transaction"); super.new(name); endfunction endclass |

記事を分けてTLMの使用例を示します。

今回は、UVMのコンポーネント間の通信で使用されるTLMについて解説しました。使用例を見ると、動作がよりイメージできると思いますので、ぜひご覧ください。