UVMの環境構築!(10) Test (テストコンポーネント)

UVMの環境構築!(9) Environment

今回は、Intel FPGAの開発ツールQuartusに同梱されたシミュレーションツールである、Questa Intel FPGA Starter Editionで、UVMが動くことを確認してみたいと思います。ソースコードやスクリプトファイルはGitHubで公開しています。

目次

Quartusバージョン21.1から、同梱されるシミュレーションツールがModelSimではなく、Questaになりました。Questa Intel FPGA Starter Editionは無償で利用可能ですが、Intelのサイトでライセンスの取得が必要になっています。

UVMの実行に関しては、ModelSimと若干の違いがありました。この記事の最後のスクリプトのところで説明します。

前回、Vivado Simulatorで試したのとまったく同じコードで動きました。

関連記事

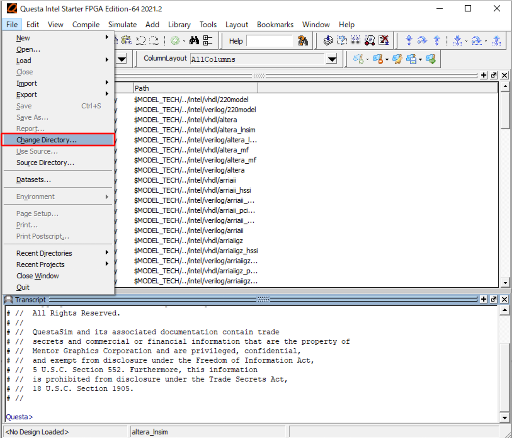

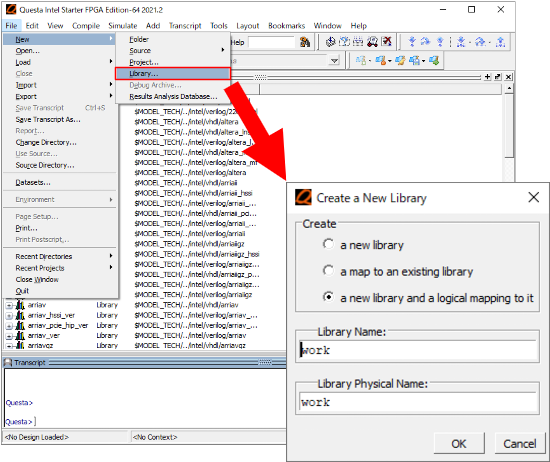

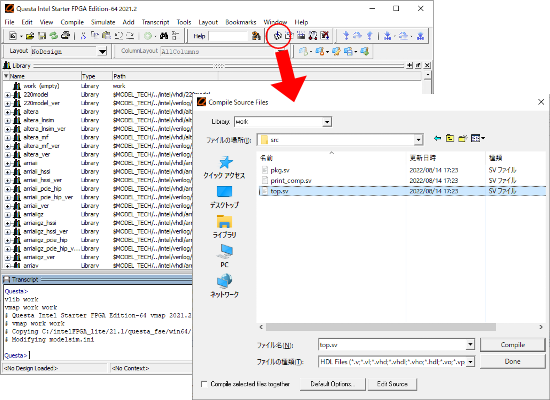

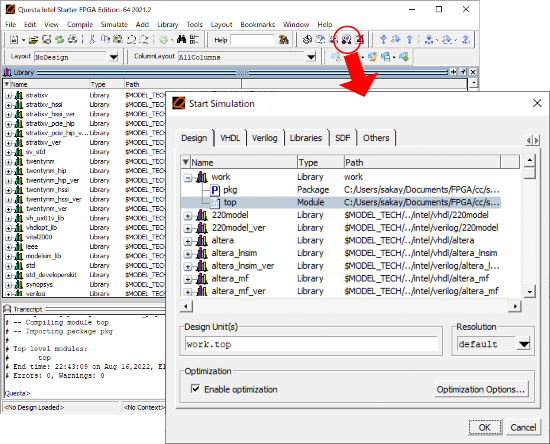

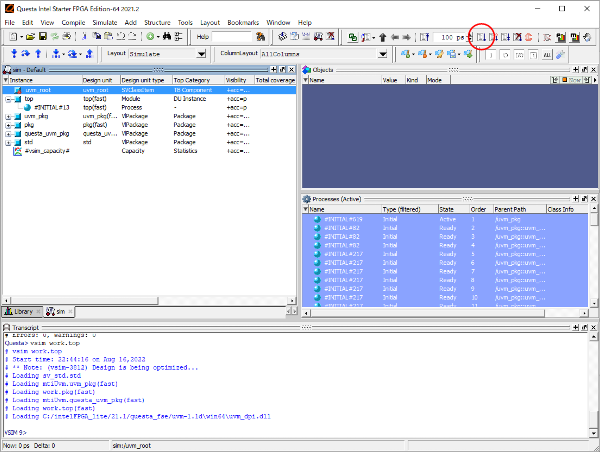

Questaを起動後、図1~図5の手順で実行します。

Transcriptウィンドウに結果が出力されています。Vivadoのときと同様に、p1は、print_comp.sv内に記述した値を出力しているのに対し、p2は、top.svで変更した値が反映され、出力されています。ちゃんと動作することが確認できました。

UVM_INFO C:/src/top.sv(14) @ 0: reporter [INFO] Simple UVM

UVM_INFO @ 0: reporter [RNTST] Running test …

UVM_INFO C:/src/print_comp.sv(25) @ 0: p1 [PRINT_COMP] i = 2, s = dog

UVM_INFO C:/src/print_comp.sv(25) @ 0: p2 [PRINT_COMP] i = 8, s = cat

— UVM Report Summary —

** Report counts by severity

UVM_INFO : 6

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[INFO] 1

[PRINT_COMP] 2

[Questa UVM] 2

[RNTST] 1

次のようなスクリプトSIMPLE_UVM.doを作成しておき、Transcriptウィンドウで、

do SIMPLE_UVM.do

とすると一発でできます。

1 2 3 4 5 6 7 8 | vlib work

vmap work work

vlog -reportprogress 300 -work work ./src/top.sv

vsim work.top

run |

なお、ModelSimではもうひと手間必要で、次のスクリプトになります。

1 2 3 4 5 6 7 8 9 10 11 12 13 | vlib work vmap work work set UVM_SRC C:/intelFPGA_lite/20.1/modelsim_ase/verilog_src/uvm-1.2/src vlog -sv $UVM_SRC/uvm.sv +incdir+$UVM_SRC $UVM_SRC/dpi/uvm_dpi.cc -ccflags -DQUESTA vmap uvm $UVM_SRC vlog -reportprogress 300 -work work ./src/top.sv -L uvm +incdir+$UVM_SRC vsim work.top run |

今回は、Questa Intel FPGA Starter EditionでUVMが動作することを確認しました。